PowerPC

維基百科,自由的 encyclopedia

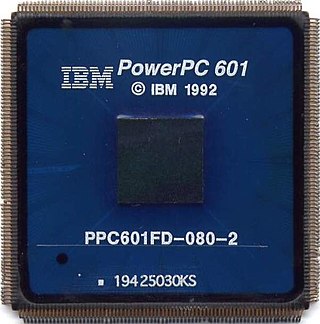

PowerPC(英語:Performance Optimization With Enhanced RISC – Performance Computing,有時簡稱PPC)是一種精簡指令集(RISC)的指令集架构 ISA(Instruction set architecture),其基本的設計源自IBM的POWER(Performance Optimized With Enhanced RISC[註 1])架構。

| 此條目可参照英語維基百科相應條目来扩充。 (2020年8月27日) |

事实速览 推出年份, 設計公司 ...

| 推出年份 | 1992年10月,31年前(1992-10) |

|---|---|

| 設計公司 | AIM |

| 最新架構版本 | 2.02 |

| 體系結構類型 | 載入-儲存 |

| 字長/暫存器資料寬度 | 32-bit/64-bit(32 → 64) |

| 位元組序 | Big/Bi |

| 指令編碼長度 | Fixed/Variable (Book E) |

| 指令集架構設計策略 | 精简指令集 |

| 擴展指令集 | AltiVec, APU |

| 分支預測結構 | Condition code(英语:Status register) |

| 32 GPR, 32 FPR | |

关闭